What is a FIFO buffer?

Since a FIFO buffer stores variable amounts of data, it will smooth out irregularities in the transfer rates of the input and output interfaces, and when used in pipeline loops, can store enough data to prevent artificial deadlocks (re: Kahn Process Networks with bounded channels).

How does FIFO handle can messages?

This is handled by hardware, so that you don't have to trigger an interrupt to service each and every CAN message. Most commonly there will be a Rx FIFO for received messages - this makes most sense since these would be causing interrupts, but some CAN controllers also support some manner of Tx FIFO.

What is the difference between FIFO buffer and mailbox?

Often FIFO is used as an adjective, e.g. a FIFO buffer is a buffer that can store multiple items and outputs them in the same order as recieved. The simplest hardware example of a FIFO buffer would probably be a shift register. The term mailbox implies some sorry of addressing scheme is in use i.e. each mailbox had a unique identifier or address.

How do you design a circular FIFO buffer (queue) in C?

How do you Design a Circular FIFO Buffer (Queue) in C? I was recently being asked by this question: How do you Design a Circular FIFO (First-In First-out) Buffer ( Queue) in C? You need to implement two methods: fifoRead and fifoWrite, which reads or writes a byte to the buffer respectively.

What is a FIFO?

What is a FIFO in a network?

What is a synchronous FIFO?

When was the first FIFO implemented?

What is FCFS in computer science?

See more

About this website

How does FIFO memory work?

FIFO means First-In First-Out. A FIFO is a structure used in hardware or software application when you need to buffer a data....Input as burst data;Output as continuous data.The FIFO is used to buffer the minimum number of burst data in order to guarantee continuous reading from FIFO without interruption.

What is FIFO interface?

The FIFO Interface coordinates data transfer. Hence, whenever a module you write passes data to another module, that data should have accompanying Valid and Ready signals.

CAN protocol mailbox?

The CAN Bus Controller with Message Filter is a full functional CAN controller module that supports the concept of mailboxes. It is compliant to the international CAN standard defined in ISO 11898-1.

What is FIFO width?

The width of the input data of the FIFO is 8 bits; however, the width of the output data is 16 bits. You use only one common clock for both read and write actions.

What is FIFO buffer?

A FIFO is a special type of buffer. The name FIFO stands for first in first out and means that the data written into the buffer first comes out of it first. There are other kinds of buffers like the LIFO (last in first out), often called a stack memory, and the shared memory.

Which data structure is FIFO?

The data structure that implements FIFO is Queue. The data structure that implements LIFO is Stack.

CAN protocol document?

1 INTRODUCTION. The Controller Area Network (CAN) is a serial communications protocol which. ... 2 BASIC CONCEPTS. CAN has the following properties. ... 3 MESSAGE TRANSFER.3.1 Frame Types. Message transfer is manifested and controlled by four different frame types: ... 3.1.1 DATA FRAME. ... 3.1.2 REMOTE FRAME.

What is asynchronous FIFO?

An asynchronous FIFO refers to a FIFO design where data values are written to a FIFO buffer from one clock domain and the data values are read from the same FIFO buffer from another clock domain, where the two clock domains are asynchronous to each other.

How is FIFO depth determined?

2:529:10Electronics Interview Questions: FIFO Buffer Depth Calculation - Part2YouTubeStart of suggested clipEnd of suggested clipNow let us calculate the FIFO depth friends in the very first step you have to calculate. The timeMoreNow let us calculate the FIFO depth friends in the very first step you have to calculate. The time taken to write one data byte. So we know module B takes two clock cycles to write one data byte

What is a buffer FPGA?

In general, clock buffers place a signal into the FPGA clock tree where it becomes an official clock of the FPGA. The clock tree consists of special paths that route clocks throughout the FPGA with low skew and low propagation delay.

Understanding FIFO: First-In, First-Out in Queue Management

Understanding FIFO: First-In, First-Out in Queue Management. If you’ve ever read anything about queues or queue management, no doubt you’ve seen this term — FIFO. Sadly, it’s got nothing to do with FIFA.

FIFO (First-In-First-Out) approach in Programming

FIFO is an abbreviation for first in, first out.It is a method for handling data structures where the first element is processed first and the newest element is processed last.. Real life example: In this example, following things are to be considered: There is a ticket counter where people come, take tickets and go.

Stored Item Counter

To distinguish between the empty and full cases, which both identically show as equal read and write counters, we also count the number of words currently stored in the FIFO.

Input Interface

The input interface inserts directly into the buffer, and only signals the other end to stop if the buffer is full.

Output Interface

The buffer output is registered, so the output interface is necessarily pipelined and works in parallel with the input interface. Keeping that pipeline full and signalling to the read_address and data_count counters when an item is removed from the buffer requires a separate little engine to continually read from the buffer when possible.

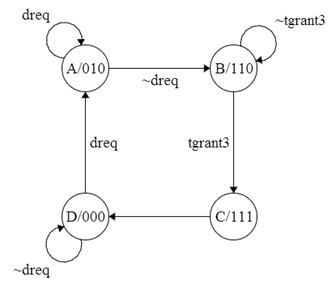

Datapath Transformations

Now that we have defined the possible states and operations of the datapath, we can define the datapath transformations, which are the edges between states. Or put otherwise: in which state (s) can the insert and/or remove operations happen, and what do they mean.

Next-State Calculations

Calculating the next state after each datapath transformation becomes the control lines of the data_count counter, where we increment, decrement, or leave constant the count of items in the buffer, which defines the state of the FIFO.

Control Signals

Here, we increment the read/write addresses as necessary (they only ever increment), enable a write to the buffer as necessary, and wrap-around the read/write addresses when they reach the end of the buffer.

What is a FIFO?

FIFOs are commonly used in electronic circuits for buffering and flow control between hardware and software. In its hardware form, a FIFO primarily consists of a set of read and write pointers, storage and control logic. Storage may be static random access memory (SRAM), flip-flops, latches or any other suitable form of storage.

What is a FIFO in a network?

Communication network bridges, switches and routers used in computer networks use FIFOs to hold data packets in route to their next destination. Typically at least one FIFO structure is used per network connection.

What is a synchronous FIFO?

Synchronicity. A synchronous FIFO is a FIFO where the same clock is used for both reading and writing. An asynchronous FIFO uses different clocks for reading and writing and they can introduce metastability issues.

When was the first FIFO implemented?

The first known FIFO implemented in electronics was by Peter Alfke in 1969 at Fairchild Semiconductor. Alfke was later a director at Xilinx .

What is FCFS in computer science?

FCFS is also the jargon term for the FIFO operating system scheduling algorithm, which gives every process central processing unit (CPU) time in the order in which it is demanded . FIFO's opposite is LIFO, last-in-first-out, where the youngest entry or "top of the stack" is processed first.

What is a FIFO?

This FIFO supports having the input and output interfaces each on their own mutually asynchronous clock (without knowledge or restriction on their relative clock frequencies or phase). Using a FIFO for data tranfer between asynchronous clock domains allows multiple transfers to overlap with the CDC synchronization overhead. Once the CDC synchronization is done, all the previously written data in one clock domain can be freely read out in the other clock domain without further overhead.

What is a FIFO depth?

Decouples two sides, each in their own asynchronous clock domain, of a ready/valid handshake to allow back-to-back transfers without a combinational path between input and output, thus pipelining the path to improve concurrency and/or timing. Any FIFO depth is allowed, not only powers-of-2. The minimum input-to-output latency is 7 cycles when both clocks are plesiochronous.

What is buffer memory?

The buffer itself is a synchronous dual-port memory with dual clocks: one write port to insert data, and one read port to concurrently remove data, each in their own clock domain. Typically this memory will be a dedicated Block RAM, but can also be built from LUT RAM if the width and depth are small, or even plain registers for very small cases. Set the RAMSTYLE parameter as required.

What is buffer in CAN?

A buffer is simply a collection of data registers that your program can access. In case of CAN, there is usually one or several "control field registers" where you can find the CAN identifier, message data length, RTR and such things. Followed by 8 bytes of the actual data.

Can buffers be stored in RAM?

Avoid these. It is possible that some microcontrollers support DMA for CAN buffers, so that you can have them stored directly in some convenient chunk of RAM, instead of having to repeatedly poll/interrupt trigger on the CAN peripheral's registers. Mailboxes is a different alternative.

What is a FIFO?

FIFOs are commonly used in electronic circuits for buffering and flow control between hardware and software. In its hardware form, a FIFO primarily consists of a set of read and write pointers, storage and control logic. Storage may be static random access memory (SRAM), flip-flops, latches or any other suitable form of storage.

What is a FIFO in a network?

Communication network bridges, switches and routers used in computer networks use FIFOs to hold data packets in route to their next destination. Typically at least one FIFO structure is used per network connection.

What is a synchronous FIFO?

Synchronicity. A synchronous FIFO is a FIFO where the same clock is used for both reading and writing. An asynchronous FIFO uses different clocks for reading and writing and they can introduce metastability issues.

When was the first FIFO implemented?

The first known FIFO implemented in electronics was by Peter Alfke in 1969 at Fairchild Semiconductor. Alfke was later a director at Xilinx .

What is FCFS in computer science?

FCFS is also the jargon term for the FIFO operating system scheduling algorithm, which gives every process central processing unit (CPU) time in the order in which it is demanded . FIFO's opposite is LIFO, last-in-first-out, where the youngest entry or "top of the stack" is processed first.